Samsung Foundry Updates: 7nm EUV, 10LPP, and 14LPC

by Joshua Ho on April 22, 2016 5:00 AM EST- Posted in

- Samsung

- 28nm

- CMOS

- Semiconductors

- Technology

- 14nm

- 10nm

Earlier this week, Samsung announced a number of updates on the foundry side of their business. While process technology might not be necessarily as interesting as the actual end product from a consumer perspective, it can often give us a good idea for what to expect in terms of performance and power from future products. Of course, it’s up to the various fabless chip design companies around the world to actually exploit the full potential of a process, but in general power and performance are often gated by process node. Almost everything in computing revolves around supporting abstractions, which inevitably means overhead to support these abstractions, so progress at the foundry level is critical for moving the industry forward as a whole.

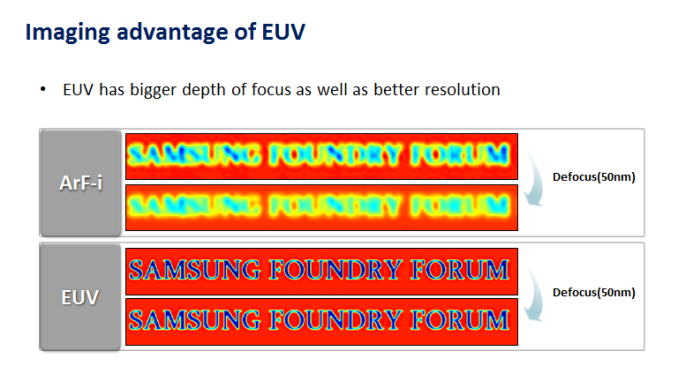

The first, and probably most important announcements are related to process roadmap. The most important point that Samsung made here was that they fully intend to deploy extreme UV (EUV) in mass production for their 7nm processes, which is a pretty significant claim to make as even imec was reluctant to say that EUV would be happening at 7nm. However, those at Samsung seem to believe that this is necessary because otherwise the first metal interconnect layer would require triple patterning, and the transistors themselves would likely be facing similar multiple patterning requirements.

While we’ve discussed EUV before and the challenges that it faces, Samsung believes that triple patterning is not really a viable solution because the number of masks needed goes from roughly 60 or so with double patterning to 90 or so with triple patterning, which results in a steep increase in costs and long lead times for prototypes and production ramp as the masks are made with e-beam lithography for precision, so mispredict penalty for a design isn’t nearly as severe as it would be with a 7nm 193i-only process. Of course, EUV is only going to be used in critical layers, so 193i will still be used for the majority of the layers in the chip, but even so EUV will still be a major hurdle for Samsung to clear here as EUV sources still don’t have enough power to be viable for mass production. Interestingly, Samsung claims that they have mask inspection tools internally for EUV masks, which could help them get to deploying EUV sooner in mass production.

On 10nm, things are less murky as it’s pretty clear that this process will be able to mostly be scaling of the 14nm node to improve performance and possibly improve cost, so the primary update here is that 10LPP (Low Power Plus) will be following 10LPE (Low Power Early) for a 10% improvement in performance. A design done in 10LPE can be directly ported to 10LPP with no new design work.

At 14nm, Samsung seems to be doing well here as their fabs in Korea and Texas are running full time, with over 0.5M wafers shipped and defect density below 0.2 defects/cm^2 in production. This defect density is said to be highly competitive, but I’m not really qualified to say whether this is the case. The primary update of note at 14nm is that 14LPC will have an RF option by the end of the year to enable connectivity for applications like automotive and transceivers.

On the process side, 28nm is still pretty critical for a number of applications as this is the last process where planar is viable. Even if 20nm is technically the last planar process, it’s not all that attractive compared to 28nm due to cost, DIBL leakage, and sheer heat density. Samsung’s 28FDS process has been in mass production for some time now as a higher-end node designed to provide ~20nm FinFET class performance on 28nm, but the main news of note here is that 28FDS will have an RF process which adds elements like inductors and is properly characterized to allow for high speed electronics to work properly. 28FDS will also have embedded non-volatile flash memory to enable embedded applications where some memory is needed as a ROM. Kelvin Low of Samsung noted that FD-SOI is also notable for reducing soft error rate relative to bulk CMOS which reduces the need for design-level mitigations, although this was mostly in the context of safety-critical systems that could be seen in automotive and other segments.

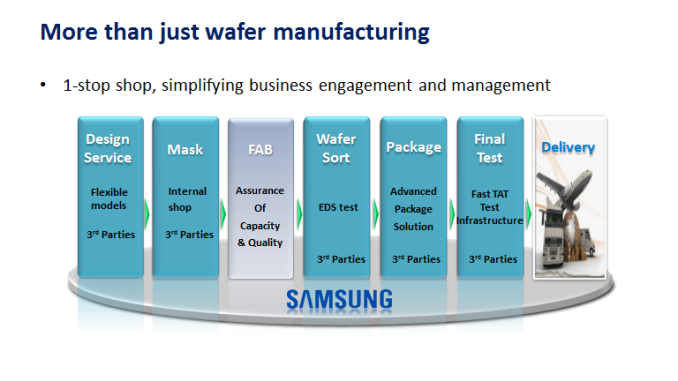

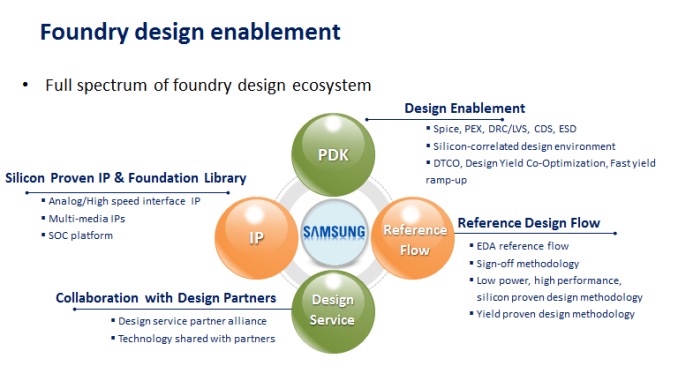

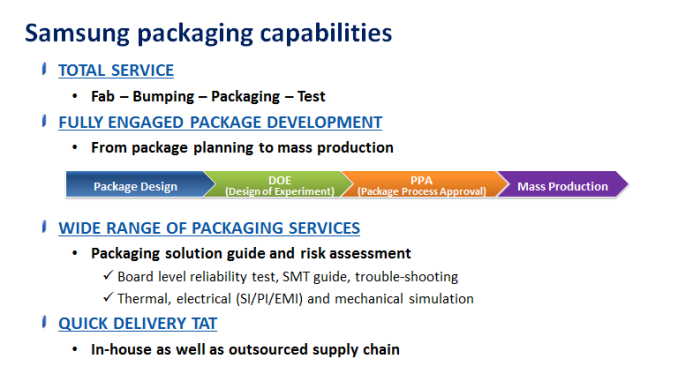

On the design and packaging services side, Samsung is providing more here than before in the form of reference design flows for their 14nm process, and a similar flow will be available for 10nm. Packaging services that used to be for internal use only will also be opened up, with things like 2.5D interposers to enable HBM on GPUs and similar use cases, although it was noted that in that particular case the interposer is currently a bit too expensive for use outside of high-priced components like GPUs. Samsung is also providing some IP blocks for customers to speed up time to market for things like DDR4 and PCI-E controllers.

Overall, Samsung is seems to be quite aggressive on the foundry side and it’ll be interesting to see whether this pays off. Of course, there are the inevitable questions of whether this is comparable to Intel or TSMC’s process, but for now we can’t really say absent details about the pitches of the key layers, operating voltages, and other aspects that we need to consider in order to really compare process nodes. We saw how Samsung’s 14nm push paid off, so it’ll be interesting to see how things shake out with 7nm.

Source: Samsung

54 Comments

View All Comments

patrickjp93 - Friday, April 22, 2016 - link

Intel's 22nm yield rate for die sizes of 450 mm sq. is 89%. Samsung doesn't even produce chips that big, and TSMC's is a measly 71%medi03 - Sunday, April 24, 2016 - link

I thought things are expensive because of huge R&D and infrastructure investments.Are material costs actualy that important in this context?

qap - Friday, April 22, 2016 - link

Well, "14nm" is only PR name. It has very little to do with real dimensions of anything. It used to be size of the smallest feature process can produce. Even if it were still true (doubt it), size of components differs. This is good example:http://pc.watch.impress.co.jp/img/pcw/docs/670/675...

extide - Friday, April 22, 2016 - link

They are close, but definitely behind Intel. See this link for a easy visual description:http://images.teraknor.net/Cell-SizeComparison.png

patrickjp93 - Friday, April 22, 2016 - link

Are you joking? http://www.eetimes.com/document.asp?doc_id=1328866It's nowhere close. Samsung's 10nm will be roughly equivalent to Intel's 14nm in density. Where Samsung currently holds an advantage is using fewer layers.

jasonelmore - Friday, April 22, 2016 - link

Intel's SRAM size is a full 20% smaller than TSMC/Samsung. This allows cache to be super small, and cache normally takes up a 1/3 of the chip. 20% is huge when cache is so prevalent in chips these days.Intel's Gate Pitch, M1 Pitch and Fin Pitch is also smaller.

https://www.semiwiki.com/forum/content/3759-intel-...

saurabhr8here - Monday, April 25, 2016 - link

The technology 'node' name used to represent the actual channel length of the transistor at 250nm and 130 nm nodes. However, that stopped being true quite a while ago (around 65nm, when the actual channel length was close to 35-40nm). Fabs kept making material changes (strain, high-K dielectrics, metal-gates, etc.) to improve performance every node while the channel length remained constant, close to 30nm for technology nodes from 45nm, down to 22nm. These are all 'Intel nodes' btw. Foundries have followed a slightly different naming convention, where they go with half-nodes such as 28nm, 20nm and 14nm. Anyway, what really matters is probably gate-pitch and metal-pitch and not the channel length or the technology node name, really.Traditionally, foundries have offered tighter metal-pitches, because they were catering to high-density low-cost SoC customers, while Intel had more aggressive transistors and poly pitches, but relaxed metal pitches because they were going for higher performance laptop/desktop/server markets. Post 20nm, Intel and foundries have completely different definitions of the technology nodes....and the 'X nm' name does not mean anything real. For example, Intel's 14nm technology node has no feature that is exactly 14nm in dimension. And the same is true for Samsung's 14nm node. They have a certain gate-pitch and metal-pitch, which give us some indication of the actual density that you can get in the technology node. however, as lithography becomes more and more difficult, printing these features become tougher and the actual density suffers. Hence, it is completely possible that you can get denser and higher-performing chips using a more relaxed gate/metal pitch combination and not scaling as fast as your competition. All these things are considered when determining the next technology node by these fabs and hence the raw dimension numbers might not match our expectations. Also, it is completely incorrect to compare two technology nodes from different companies just based on a few dimensional parameters.

In short, it is completely true that Samsung's 14nm/10nm/7nm definition is unequal/different to Intel's. And so is TSMC's too...so all three foundries end up with different definitions and the only way to compare them is to look at power/performance/area/cost trends of taped-out chips.

Michael Bay - Friday, April 22, 2016 - link

>Samsung>eliminated the gap

>AMD being ahead of Intel in anything

Nice stuff, leave some for me.

medi03 - Sunday, April 24, 2016 - link

AMD APUs are way ahead of Intel at gaming.negusp - Sunday, May 8, 2016 - link

lol not anymore. The HD 520 is faster than pretty much all AMD offerings in their normal APUs and the Iris Graphics blow the rest to pot. In addition, quite a few games are CPU-limited and Intel is just so much faster.