Hot Chips 2020 Live Blog: Microsoft Xbox Series X System Architecture (6:00pm PT)

by Dr. Ian Cutress on August 17, 2020 9:00 PM EST- Posted in

- CPUs

- Microsoft

- GPUs

- Xbox

- Live Blog

- Xbox Series X

- Hot Chips 32

09:04PM EDT - Final talk of the day is Xbox Series X System Architecture!

09:05PM EDT - Azure Silicon Architecture Team

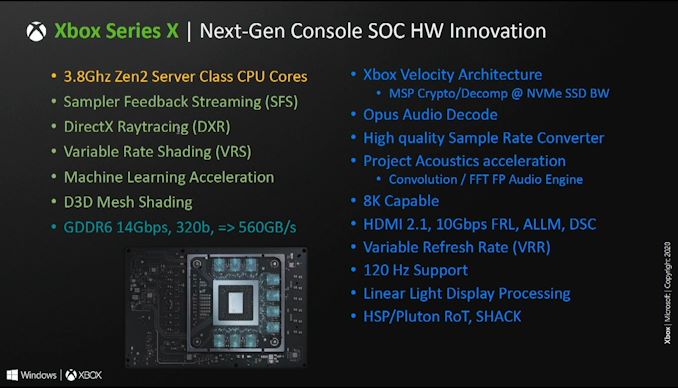

09:06PM EDT - 3.8 GHz Zen2 Server cores

09:06PM EDT - DXR, VRS, Machine LEarning Acceleration

09:07PM EDT - 14 Gbps GDDR6, 320-bit = 560 GB/s

09:07PM EDT - Hardware accelerators in blue

09:07PM EDT - 120 Hz support, VRR, Xbox Velocity Architecture for MSP Crypto/Decomp on NVMe SSD

09:07PM EDT - Acoustic acceleration

09:07PM EDT - HSP/Pluton RoT - security

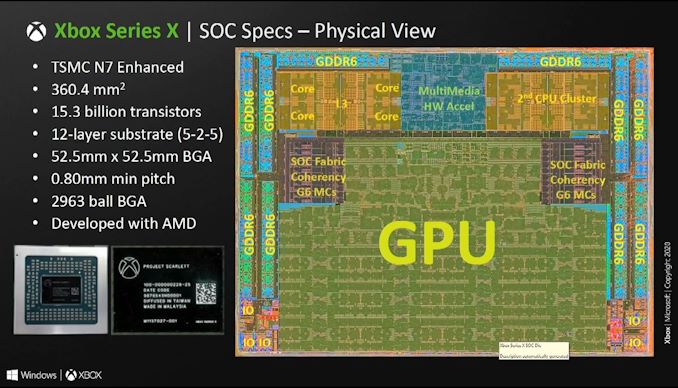

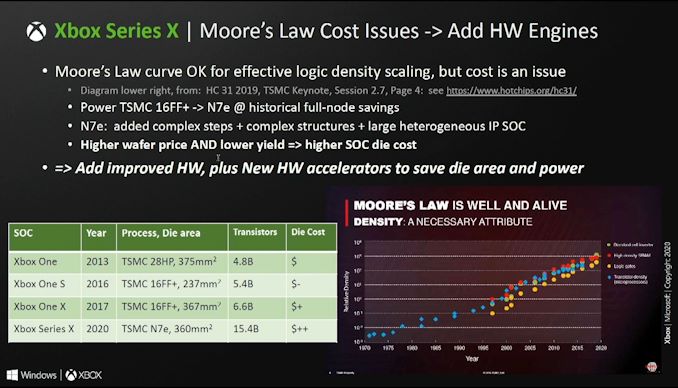

09:08PM EDT - 360.4mm2 TSMC N7 enhanced

09:08PM EDT - 15.3B transistors

09:08PM EDT - 2 four core CPU clusters

09:08PM EDT - 10 GDDR6 controllers

09:09PM EDT - GPU 12 FLOPs

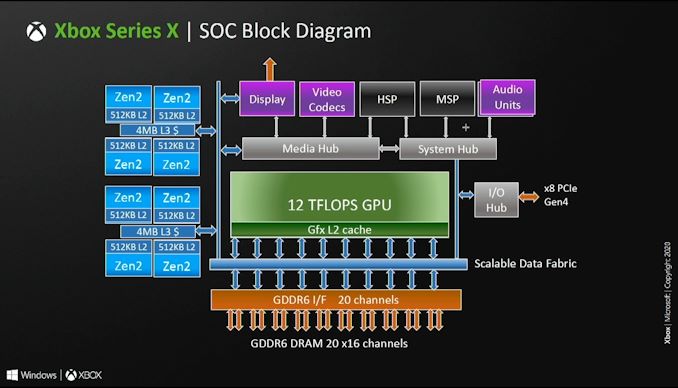

09:10PM EDT - AVX256 gives 972 GFLOP over CPU

09:10PM EDT - 16 GB of GDDR6 total

09:11PM EDT - >Says Zen2 server class, but L3 cache is mobile class?

09:11PM EDT - Display processing is kept off the shader engines

09:11PM EDT - IO hub supports PCIe 4.0 x8

09:11PM EDT - Operates on linear light values, not gamma light values

09:12PM EDT - ALLM - Auto Low Latency Mode

09:13PM EDT - Increased die cost on this APU over previous generation

09:13PM EDT - Significantly more expensive!

09:13PM EDT - Trade off

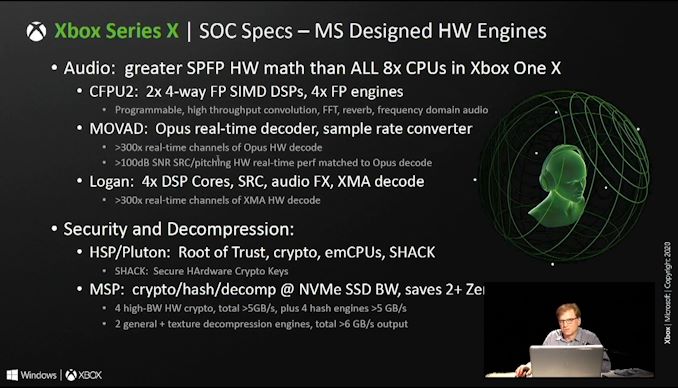

09:13PM EDT - MS created Audio engines - 3 engines, CFPU2, MOVAD, LOGAN

09:13PM EDT - CFPU2 for audio convolution, FFT, reverb

09:14PM EDT - such as Project Acoustics to model 3D audio sources

09:14PM EDT - MOVAD - hyper real-time hardware audio decoder

09:14PM EDT - >300x channels decode at once

09:14PM EDT - best trade off codec, so made in hardware

09:15PM EDT - >100dB signal noise ratio

09:15PM EDT - HW realtime real-time matched to decode based on sampling

09:15PM EDT - Logan is offering also better offload in traditional modes

09:15PM EDT - HSP/Pluton: Root of trust, crypto, SHACK (crypto keys)

09:15PM EDT - MSP supports 5 GB/s high-bw crypto on the SSD

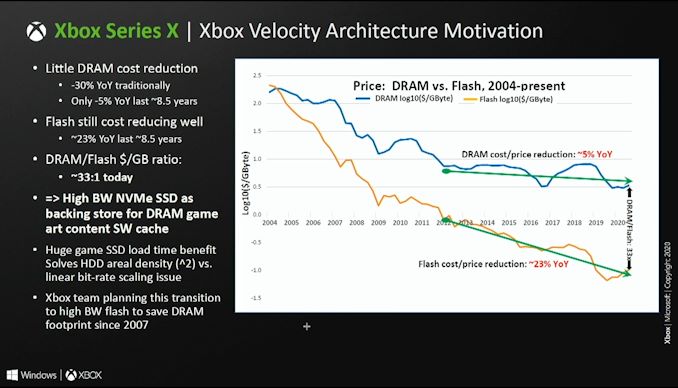

09:16PM EDT - DRAM to SSD balance needed for refill

09:16PM EDT - Load times are always increasing unless SW-to-DRAM bw increases, hence NVMe SSDs

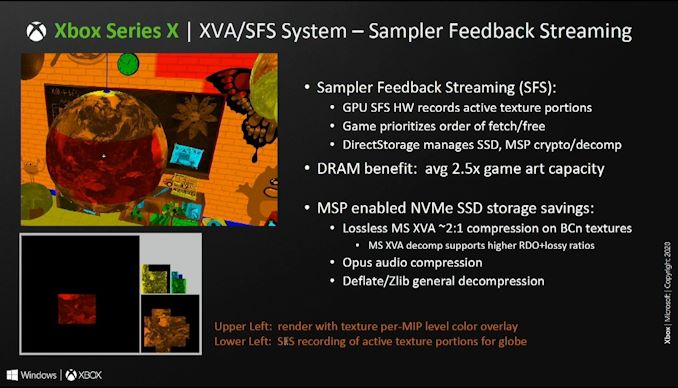

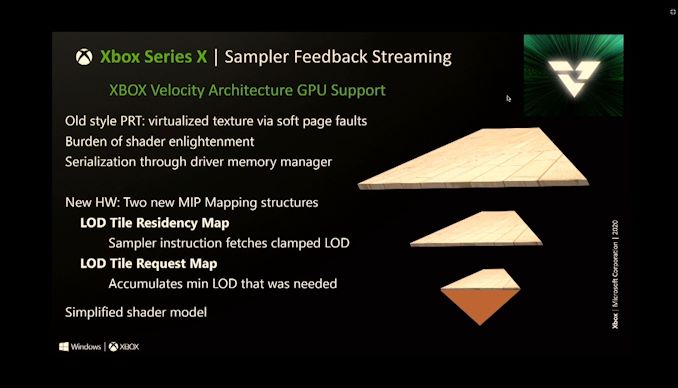

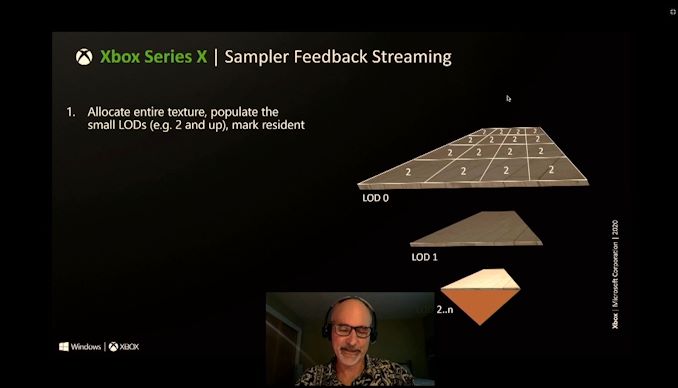

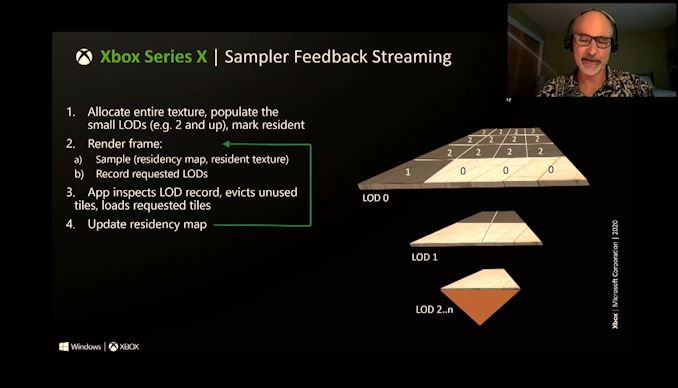

09:17PM EDT - Sampler Feedback System

09:17PM EDT - New metadata for texture portions to pre-load texture caches

09:17PM EDT - Direct Storage

09:17PM EDT - Manages data locations ahead of developer

09:18PM EDT - Distinct savings for most detail texture maps savings

09:18PM EDT - Lossless MS XVA 2:1 compression

09:19PM EDT - Need big GPU - get the tech out of the way

09:19PM EDT - Need raw ops/second increase within PPA and cost

09:19PM EDT - 12.2 supported in HW

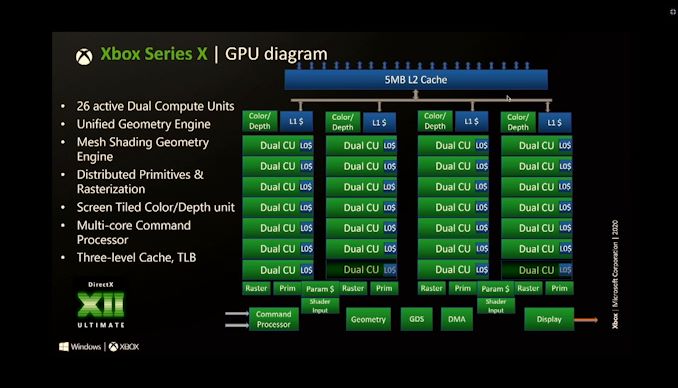

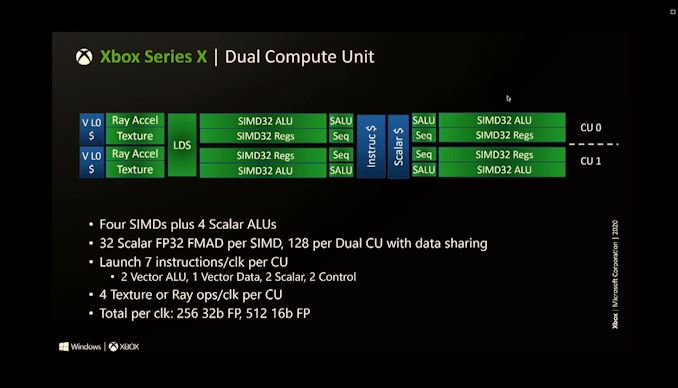

09:19PM EDT - 26 active dual CUs (52 CUs)

09:20PM EDT - single geometry supports primatives

09:20PM EDT - DIrectly snoop CPU caches

09:20PM EDT - Dual stream multi-core command processor

09:20PM EDT - Double rate 16-bit math

09:20PM EDT - single cycle issue rate to reduce stalls

09:21PM EDT - CUs have 25% better perf/clock compared to last gen

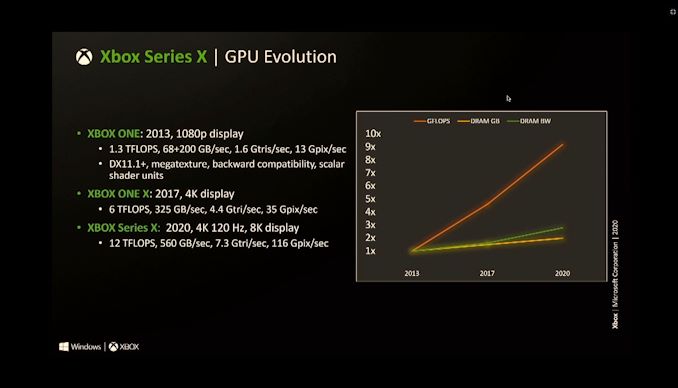

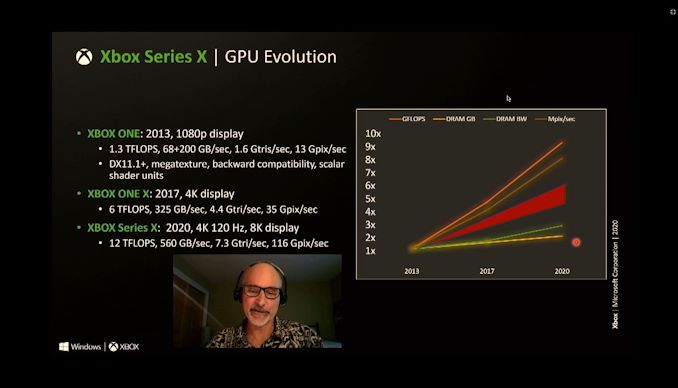

09:21PM EDT - GPU Evolution: FLOPS have outpaced mem space and BW

09:21PM EDT - Screen pixels has increased in th emiddle

09:22PM EDT - How to fill pixels better without blowing power budget

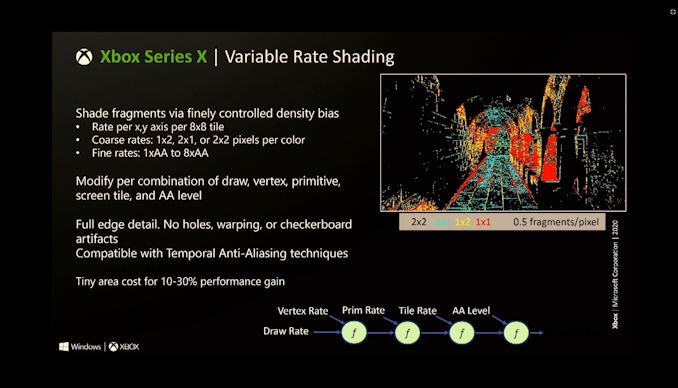

09:22PM EDT - VRS

09:22PM EDT - supports up to 2x2

09:22PM EDT - 10-30% perf gain for tiny area cost

09:23PM EDT - Full edge detail

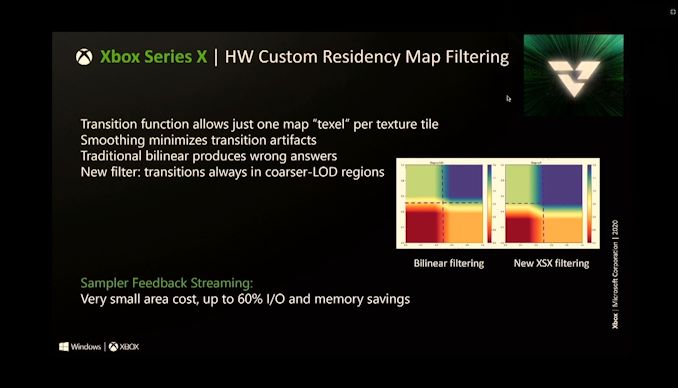

09:23PM EDT - SFS

09:24PM EDT - Previously very slow to enable

09:24PM EDT - Two new HW structures for tile-by-tile management for in-DRAM textures

09:25PM EDT - clamps LOD

09:26PM EDT - Tilemaps should stay on die for best latency

09:27PM EDT - SFS: 60% IO/Mem savings for small die area cost

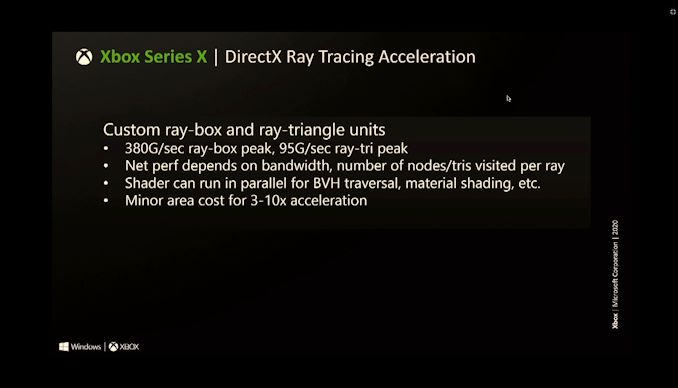

09:27PM EDT - DX Ray Tracing Accel

09:27PM EDT - Not a complete replacement - RT can be applied selectively based on traditional models

09:28PM EDT - Custom ray-triangle units

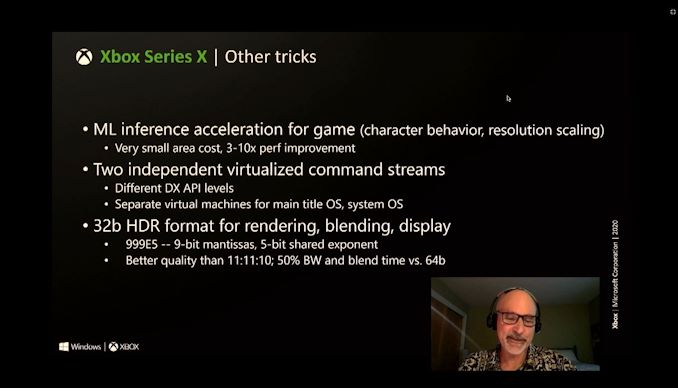

09:28PM EDT - ML inference

09:29PM EDT - Two virtualized command streams - two VMs

09:29PM EDT - Main title OS vs system OS

09:29PM EDT - 32b HDR rendering, blending display

09:29PM EDT - Optimized games. Unable to show at the event

09:30PM EDT - Q&A Time

09:31PM EDT - Q: TDP? A: Not commenting. There's so many things that are involved in the TDP, and tradeoffs. We're not really able to descibe it without describing it in a technical environemtn

09:32PM EDT - Q: Can you stream into the GPU cache? A: Lots of programmable cache modes. Streaming modes, bypass modes, coherence modes.

09:33PM EDT - Q: Coherency CPU and GPU? A: GPU can snoop CPU, reverse requires software

09:35PM EDT - Q: Are you happy as DX12 as a low hardware API? A: DX12 is very versatile - we have some Xbox specific enhancements that power developers can use. But we try to have consistency between Xbox and PC. Divergence isn't that good. But we work with developers when designing these chips so that their needs are met. Not heard many complains so far (as a silicon person!). We have a SMASH driver model. The games on the binaries implement the hardware layed out data that the GPU eats directly - it's not a HAL layer abstraction. MS also re-writes the driver and smashes it together, we replace that and the firmware in the GPU. It's significantly more efficient than the PC.

09:35PM EDT - Q: Is link between CPU and GPU clocks? A: Hardware is independent.

09:36PM EDT - Q: Is the CPU 3.8 GHz clock a continual or turbo? A: Continual.

09:36PM EDT - Continual to minimize variance

09:37PM EDT - Q: TSMC 7nm enhanced, is it N7P, N7+, or something else? A: It's not base 7nm, it's progressed over time. Lots of work between AMD and TSMC to hit our targets and what we needed

09:38PM EDT - Q: Says Zen 2 is server class, but you use L3 mobile class? A: Yeah our caches are different, but I won't say any more, that's more AMD.

09:39PM EDT - Q: With 20 channels GDDR6, is that really cheaper than 2 stacks HBM? A: We're not religious about which DRAM tech to use. We needed the GPU to have a ton of bandwidth. Lots of channels allows for low latency requests to be serviced. HBM did have an MLC model thought about, but people voted with their feet and JEDEC decided not to go with it.

09:40PM EDT - Q: GDDR6 on sides, not bottom? A: bottom is power, how board interfaces with the chip. GPU has high EDC and currents, and you need clean copper to deliver that. With that much current you need to leave that space unless you use super expensive packaging. We did it the cost efficient way

09:41PM EDT - Q: Why do you need so much math for audio processing? A: 3D positional audio and spatial audio and real world spaces if you 300-400 audio sounds positional in 3D and want to start doing other effects on all samples, it gets very heavy compute. Imagine 20 people fighting in a cave and reflections with all sorts of noises

09:43PM EDT - That's a wrap and we're done for today. Come back tomorrow at 8:30am PT to talk about FPGAs. It's 2:44am here in the UK, time to go to bed.

58 Comments

View All Comments

NixZero - Tuesday, August 18, 2020 - link

it is possible that by reducing memory speed they can get better latency for cpu access, as gddr6 is optimized for througput so not ideal for cpu use.drothgery - Tuesday, August 18, 2020 - link

RAM cost, as they pretty much made clear in the presentation, but I wouldn't be surprised at all if 2023-2024 mid-generation update ups it 20 GB if DRAM prices drop enough.Eliadbu - Tuesday, August 18, 2020 - link

cost, they are paying good penny for the SoC and SSD already, faster and bigger memory means additional $ and in console where you very slim profit margins if any at all, saving those bucks means a lot.6YearsLater - Tuesday, August 18, 2020 - link

“CUs have 25% better perf/clock compared to last gen”.So, what does this mean?What is so called "last gen"?Last generation platform(Polaris)?Or RDNA1?

Eliadbu - Tuesday, August 18, 2020 - link

Microsoft is not AMD so when they compare generation they compare their hardware meaning last generation console. but they should be clear what is performance metric, FP? fps in games ? or something else ?Spunjji - Wednesday, August 19, 2020 - link

I'm guessing they're comparing to Polaris in the Xbox One X; the rest of the performance difference would be down to increased clocks.brucethemoose - Tuesday, August 18, 2020 - link

Holy moly that audio hardware. I hope we get some kind of accelerator with all that on PC.brucethemoose - Tuesday, August 18, 2020 - link

Also, I wish they mentioned something about videobcodecs. AV1 or no AV1 in the consoles and RDNA2 is a pretty big deal.RedOnlyFan - Tuesday, August 18, 2020 - link

From the transistor count and die size the TSMCs 7+ nm density doesn't add up. 42M/mm2. GPU are more efficient density right??psychobriggsy - Tuesday, August 18, 2020 - link

Yeah, 42.8 MTr/mm^2 is a bit low given that Renoir can hit 60MTr/mm^2 already. Is 7nm Enhanced actually N7+ EUV however? It might just be N7P. I know this doesn't fit in with what people expected, but with that density...Maybe it is using higher-performance larger transistors in a lot of areas.