IBM Creates First 2nm Chip

by Dr. Ian Cutress on May 6, 2021 6:00 AM EST

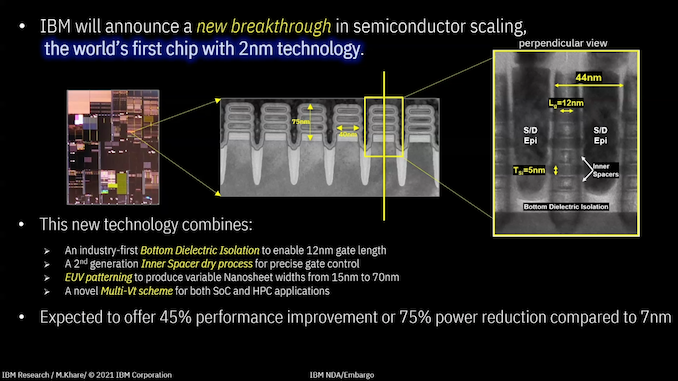

Every decade is the decade that tests the limits of Moore’s Law, and this decade is no different. With the arrival of Extreme Ultra Violet (EUV) technology, the intricacies of multipatterning techniques developed on previous technology nodes can now be applied with the finer resolution that EUV provides. That, along with other more technical improvements, can lead to a decrease in transistor size, enabling the future of semiconductors. To that end, Today IBM is announcing it has created the world’s first 2 nanometer node chip.

Names for Nodes

Just to clarify here, while the process node is being called ‘2 nanometer’, nothing about transistor dimensions resembles a traditional expectation of what 2nm might be. In the past, the dimension used to be an equivalent metric for 2D feature size on the chip, such as 90nm, 65nm, and 40nm. However with the advent of 3D transistor design with FinFETs and others, the process node name is now an interpretation of an ‘equivalent 2D transistor’ design.

Some of the features on this chip are likely to be low single digits in actual nanometers, such as transistor fin leakage protection layers, but it’s important to note the disconnect in how process nodes are currently named. Often the argument pivots to transistor density as a more accurate metric, and this is something that IBM is sharing with us.

Transistor Density

Today’s announcement states that IBM’s 2nm development will improve performance by 45% at the same power, or 75% energy at the same performance, compared to modern 7nm processors. IBM is keen to point out that it was the first research institution to demonstrate 7nm in 2015 and 5nm in 2017, the latter of which upgraded from FinFETs to nanosheet technologies that allow for a greater customization of the voltage characteristics of individual transistors.

IBM states that the technology can fit ’50 billion transistors onto a chip the size of a fingernail’. We reached out to IBM to ask for clarification on what the size of a fingernail was, given that internally we were coming up with numbers from 50 square millimeters to 250 square millimeters. IBM’s press relations stated that a fingernail in this context is 150 square millimeters. That puts IBM’s transistor density at 333 million transistors per square millimeter (MTr/mm2).

For comparison:

| Peak Quoted Transistor Densities (MTr/mm2) | ||||

| AnandTech | IBM | TSMC | Intel | Samsung |

| 22nm | 16.50 | |||

| 16nm/14nm | 28.88 | 44.67 | 33.32 | |

| 10nm | 52.51 | 100.76 | 51.82 | |

| 7nm | 91.20 | 237.18* | 95.08 | |

| 5nm | 171.30 | |||

| 3nm | 292.21* | |||

| 2nm | 333.33 | |||

| Data from Wikichip, Different Fabs may have different counting methodologies * Estimated Logic Density |

||||

As you can tell, different foundries have different official names with a variety of densities. It’s worth noting that these density numbers are often listed as peak densities, for transistor libraries where die area is the peak concern, rather than frequency scaling – often the fastest parts of a processor are half as dense as these numbers due to power and thermal concerns.

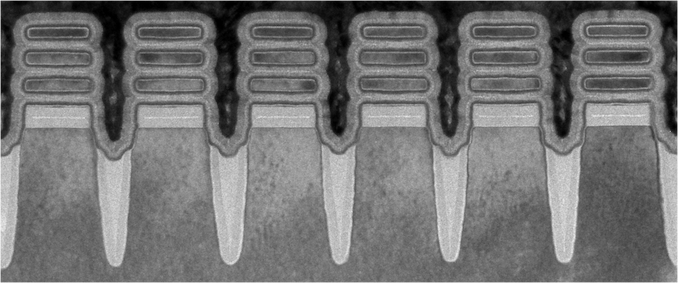

With regards the movement to Gate-All-Around / nanosheet transistors, while not explicitly stated by IBM, images show that this new 2nm processor is using a three-stack GAA design. Samsung is introducing GAA at 3nm, while TSMC is waiting until 2nm. Intel by contrast, we believe, will introduce some form of GAA on its 5nm process.

IBM’s 3-stack GAA uses a cell height of 75 nm, a cell width of 40 nm, and the individual nanosheets are 5nm in height, separated from each other by 5 nm. The gate poly pitch is 44nm, and the gate length is 12 nm. IBM says that its design is the first to use bottom dieletric isolation channels, which enables the 12 nm gate length, and that its inner spacers are a second generation dry process design that help enable nanosheet development. This is complimented by the first use of EUV patterning on the FEOL parts of the process, enabling EUV at all stages of the design for critical layers.

Users might be wondering why we’re hearing that IBM is the first to a 2nm chip. IBM is one of the world’s leading research centers on future semiconductor technology, and despite not having a foundry offering of their own, IBM develops IP in collaboration with others for their manufacturing facilities. IBM sold its manufacturing to GlobalFoundries with a 10 year partnership commitment back in 2014, and IBM also currently works with Samsung, and recently announced a partnership with Intel. No doubt the latter two will be partnering with IBM on some level around this new development for its viability in their own production chain.

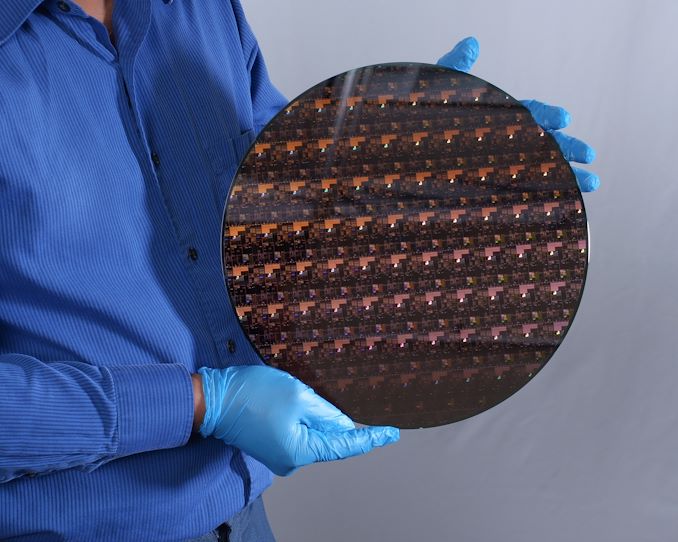

No details on the 2nm test chip have been provided, although at this stage it is likely to be a simplified SRAM test vehicle with a little logic. The 12-inch wafer images showcase a variety of different light diffractions, which likely points to a variety of test cases to affirm the viability of the technology. IBM says that the test design uses a multi-Vt scheme for high-performance and high-efficiency application demonstrations.

The chip was designed and made at IBM’s Albany research facility, which features a 100,000 sq. ft. clean room. The purpose of this facility is to build on IBM’s expansive patent and licensing portfolio for collaborations with partners.

We have a set of questions with IBM’s experts awaiting response. We also now have an active invitation to go visit, as and when we can travel again.

Related Reading

- IBM and AMD to Advance Confidential Computing

- Hot Chips 2020 Live Blog: IBM z15, a 5.2 GHz Mainframe CPU (11:00am PT)

- IBM & Partners to Fight COVID-19 with Supercomputers, Forms COVID-19 HPC Consortium

- Hot Chips 31 Live Blogs: IBM's Next Generation POWER

- IBM to use Samsung 7nm EUV for Next-Gen POWER and z CPUs

- IBM And Everspin Announce 19TB NVMe SSD With MRAM Write Cache

- TSMC Update: 2nm in Development, 3nm and 4nm on Track for 2022

- Intel’s Manufacturing Roadmap from 2019 to 2029: Back Porting, 7nm, 5nm, 3nm, 2nm, and 1.4 nm

118 Comments

View All Comments

michael2k - Thursday, May 6, 2021 - link

You contradict yourself.Intel doesn't have a 7nm process to compare to TSMC's 5nm, hence Intel is behind by your very own logic. Trying to argue high powered vs low powered doesn't have any value when Intel has neither high nor low powered at 7nm. If Intel's HP 5nm is a 2023 design and TSMC's LP 5nm N5P (their second iteration of N5) is a late 2020 design, that's a 3 year gap. And given Intel might still hit delays, even 3 years might be optimistic; it could be 4 years.

N5 was a 15% improvement in performance over N7, and N5P is a 23% improvement in performance over N7, holding power steady.

Yojimbo - Friday, May 7, 2021 - link

"Intel doesn't have a 7nm process to compare to TSMC's 5nm, hence Intel is behind by your very own logic."Intel's 7nm is beyond TSMC's 5 nm. Of course they have one. Stop trying to sound fancy "by your own logic". It doesn't make any sense.

Neither TSMC nor Intel are producing large, high volume, high powered chips on 5 (TSMC) or 7 (Intel) nm at the moment. But that doesn't mean they don't have them. They have those respective processes. We just don't know what state they are in. But the idea that we can talk about what will comin in the future with TSMC but not with Intel because, because why? because you prefer it that way? Because TSMC is producing low voltage chips on 5 nm?

We are talking about the future here, about expectations. That goes for both Intel and TSMC. It's normal to talk about expectations. It doesn't lead to a logical contradiction or to a black hole that swallows us all.

You are again comparing apples and oranges by talking about when Intel will release a large volume of large, high voltage chips to when TSMC began high volume manufacturing of small, low voltage chips. No matter how much you want to stamp your feet and insist, that is an improper comparison. Intel isn't even completing in your competition.

"N5 was a 15% improvement in performance over N7, and N5P is a 23% improvement in performance over N7, holding power steady."

And that less than stellar improvement is exactly what allows Intel to move from being 1 1/2 years behind to close to even.

Yojimbo - Friday, May 7, 2021 - link

*Intel isn't even competing in your competition.michael2k - Friday, May 7, 2021 - link

Intel has no shipping 7nm products.Intel planned to turn Fab 42 into a 7nm node in 2017, but is currently a 10nm node.

Intel has already told shareholders that 7nm will be delayed until 2022:

https://hexus.net/tech/news/cpu/144355-intel-q2-ea...

They expect tape-in Q2Y21, so they will probably hit 2022 or 2023 for scale release of 7nm:

https://www.intel.com/content/www/us/en/newsroom/n...

Regarding large, high volume, high powered chips:

TSMC is shipping an 88 sqmm A14 with 11.8b transistors and 120 sqmm M1 with 16b transistors.

The two easily resulted in tens of millions of sales these past two quarters (and nearly 10 million the very first weekend the iPhone 12 was available!)

You can compare to Intel's 10nm die sizes, as reported by Anandtech:

https://www.anandtech.com/show/15380/i-ran-off-wit...

Ice Lake 122 sqmm for a quad core part.

Tiger Lake 145 sqmm for a quad core part.

You're trying to create an imaginary boundary (Not me, but you) to say TSMC isn't competing with Intel because TSMC is shipping small, low voltage chips that can't compare to Intel's non shipping similarly sized similarly low voltage chips.

You keep trying to claim Intel is catching up. Fine, in late 2022 to early 2023, Intel will catch up to TSMC. I don't disagree they will catch up, after all, because that is the proof that they are behind.

Yojimbo - Friday, May 7, 2021 - link

Intel will ship 7 nm parts in 2023. That's when they will be close to even. The M1 chips are not large, high voltage parts. The A14 is certainly not. Again, you are not considering the differences in the businesses of Apple, TSMC, and Intel.How about this. In 2023 compare Intel's 7nm chips to AMD's competing chips at the time, and wonder how if TSMC is so far ahead of Intel that Intel is suddenly on par with AMD again? Then when you want to figure out the mystery, come back and read my messages. On the other hand you say you don't disagree with that, so I don't know why you've spent so much time arguing against it.

"...because that is the proof they are behind"

This is a strange thing to say..as if your pleasure in life is that Intel is behind. I started out by saying that Intel is behind. You said they were 3 years behind, I said they were 1 1/2 years behind. You first said they won't catch up, now you say they will catch up 3 years worth of time in 2 years. I say they will catch up 1 1/2 years worth of time in 2 years.

Guspaz - Saturday, May 8, 2021 - link

How do you define large? M1 is a 120 sqm die, half again larger than a Zen 3 chiplet. M1X/M2 is expected to be a fair bit larger. If you adjust for the difference in density (TSMC 5nm is ~4.57x as dense as Intel 14nm), M1 is more than double the size of Intel's biggest desktop Rocket Lake CPU.Intel's 7nm process is moderately higher density than TSMC's 5nm, but TSMC will be in mass production of their 3nm process (late 2021/early 2022) around a year before Intel's 7nm, and that's much more comparable (TSMC is then ~10% denser, so pretty close). So I'd say that if Intel's 7nm is on time, they'll have narrowed the gap, and they will only be a year and a half behind when 7nm hits mass production. If Intel's 7nm sees more delays, that's another story.

michael2k - Monday, May 10, 2021 - link

You're really playing this game?Today: Intel ships no 7nm, TSMC ships 5nm, ergo Intel's target 2023 date puts them 3 years behind TSMC

Today: M1 chips are large, at 120 sqmm. It runs as high a voltage as needed to hit 3.2GHz, by design, as any more is a waste of power. Intel, also by design, varies voltage up to clock higher. An i7 scales voltage to hit different frequencies (an 1185 scales between 12W to 28W, 1 core to 4 cores, 1.2GHz to 4.4GHz) The A14, similar to the M1, can run all cores at 96% of max speed; lon story short, it doesn't matter that M1 chips aren't high voltage, because Apple can beat Intel's performance today with lower voltage parts.

So, no we aren't going to compare 2023 parts because it isn't 2023. We are comparing 2021 parts because it's 2021. Right now Intel is 3 years behind as their competing 7nm parts won't be available until 2023, 3 years after the competitive and competing 5nm M1 was released.

Disagree isn't even the point. You're speculating on a part that doesn't exist yet. It could be 2024, making Intel 4 years behind, for example.

As for pleasure, yeah, I enjoy the technical details and I'm technically right. Until Intel ships they are behind. How far behind? We both agree 2023 is a reasonable target, and when that occurs we can compare which technology stack is most similar. Of course, 2023 is also the target date for TSMC's 3nm node, which would mean Intel won't have caught up even then because the 3nm node is ever so slightly more dense than Intel's 7nm, though at least it is far more competitive than comparing Intel 14nm to TSMC 10nm, or Intel 10nm to TSMC 7nm

Spunjji - Friday, May 7, 2021 - link

There's a lot of special pleading involved here that, on closer inspection, doesn't make sense.Your insistence on only counting a node as /really/ launching when it supports high-powered chip production is pretty arbitrary, and penalises TSMC for its partners' decisions about when to move to the newest processes. By the same token it favours Intel, who have every incentive to start pushing designs on their latest processes even when they're not performing or yielding very well (e.g. Ice Lake on 10nm+), because they are their own biggest customer.

Let's look at like-for-like. If you're counting Intel's 10nm as having been online since Ice Lake launched in September 2019 (as Intel do - RIP Cannon Lake) then by those same standards TSMC 5nm has been online since November 2020. The numbers:

Ice Lake on Intel's 10nm+ is ~122.52 mm² at a ~15-28W TDP.

M1 on TSMC N5 is ~120.5 mm² at a ~10-25W TDP.

On the other hand, if the benchmark for a process coming online is volume production of large / high power dies, then Intel 10nm+ only actually came online with Ice Lake SP in April 2021, starting at 370mm² with the LCC die. 10nm+ is arguably inferior to TSMC N7, and AMD launched Vega VII at 330mm² on N7 back in February 2019 - by your "big die" standard, that puts Intel around 2 years and 2 months behind TSMC on the current most relevant nodes. That's a fair bit of catching up to do.

If Intel 7nm arrives in 2023, and if it is roughly a half node ahead of TSMC 5nm (I'd expect that it will be), that's still arriving roughly a year behind TSMC's N3 and 18 months behind their N4 which ought to be roughly comparable (unless N4 sucks and 7nm rocks, which is possible!).

So: if Intel and TSMC hit their targets, Apple keep executing early on TSMC's new nodes, and Intel launch their new process with U-class chips, then on a like-for-like basis Intel will still be roughly 18 months behind TSMC when 7nm launches.

TL;DR: I don't agree with your thesis that Intel are catching up as much as you say, because you've cooked the books on the comparison between nodes by moving the goalposts on what you're comparing.

Exotica - Thursday, May 6, 2021 - link

Intel’s 10nm transistor density is looking quite impressive compared to TSMC and Samsung 7nm.duploxxx - Thursday, May 6, 2021 - link

you can call it impressive, but if it ain't scaling performance wise and quality wise than what is the added value?