Marvell Announces First PCIe 5.0 NVMe SSD Controllers: Up To 14 GB/s

by Billy Tallis on May 27, 2021 8:30 AM EST

Today Marvell is announcing the first NVMe SSD controllers to support PCIe 5.0, and a new branding strategy for Marvell's storage controllers. The new SSD controllers are the first under the umbrella of Marvell's Bravera brand, which will also encompass HDD controllers and other storage accelerator products. The Bravera SC5 family of PCIe 5.0 SSD controllers will consist of two controller models: the 8-channel MV-SS1331 and the 16-channel MV-SS1333.

| Marvell Bravera SC5 SSD Controllers | ||||||

| MV-SS1331 | MV-SS1333 | |||||

| Host Interface | PCIe 5.0 x4 (dual-port x2+x2 capable) | |||||

| NAND Interface | 8ch, 1600 MT/s | 16ch, 1600 MT/s | ||||

| DRAM | DDR4-3200, LPDDR4x-4266 with ECC | |||||

| Sequential Read | 14 GB/s | |||||

| Sequential Write | 9 GB/s | |||||

| Random Read | 2 M IOPS | |||||

| Random Write | 1 M IOPS | |||||

| Max Controller Power | 8.7 W | 9.8 W | ||||

| Virtualization | 16 Physical Functions, 32 Virtual Functions | |||||

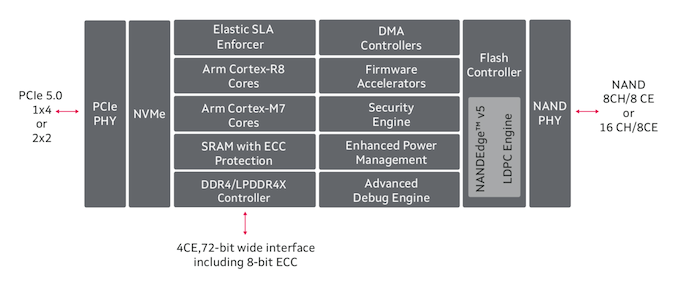

These new SSD controllers roughly double the performance available from PCIe 4.0 SSDs, meaning sequential read throughput hits 14 GB/s and random read performance of around 2M IOPS. To reach this level of performance while staying within the power and thermal limits of common enterprise SSD form factors, Marvell has had to improve power efficiency by 40% over their previous generation SSD controllers. That goes beyond the improvement that can be gained simply from smaller fab process nodes, so Marvell has had to significantly alter the architecture of their controllers. The Bravera SC5 controllers still include a mix of Arm cores (Cortex-R8, Cortex-M7 and a Cortex-M3), but now includes much more fixed-function hardware to handle the basic tasks of the controller with high throughput and consistently low latency.

Such an architectural shift often means sacrificing flexibility, but Marvell doesn't expect that to be a problem thanks in large part to the Open Compute Project's Cloud SSD specifications. Those standards go beyond the NVMe spec and define which optional features should be implemented, plus target performance and power levels for different form factors. The Cloud SSD specs were initially a collaboration between Microsoft and Facebook but have caught on in the broader market and even have the support of traditional enterprise server vendors like Dell and HP. This allows controller vendors like Marvell and SSD manufacturers to more narrowly focus their product development efforts, and to target a wider range of customers with a single hardware and firmware platform. In spite of the shift toward more fixed hardware functionality, the Bravera SC5 controllers still support a wide range of features including NVMe Zoned Namespaces (ZNS), Open Channel SSDs and Kioxia's Software-Enabled Flash model.

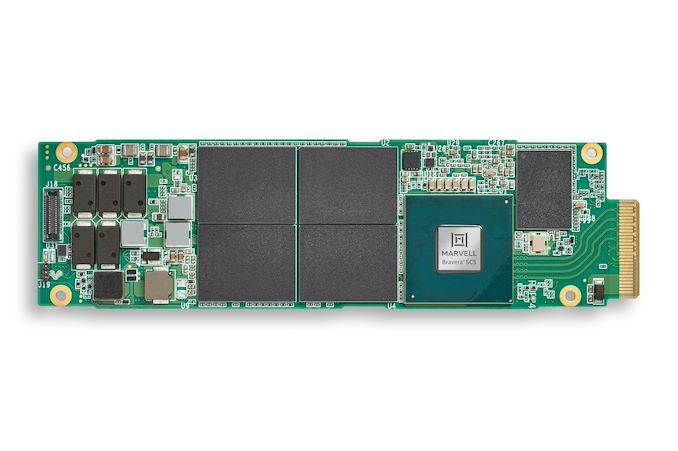

In addition to being the first available PCIe 5.0 SSD controllers, the Bravera SC5 family includes the first 16-channel controller designed to fit on the EDSFF E1.S form factor, using a controller package size of 20x20 mm with peak controller power of 9.8 W. The new controllers are currently sampling to select customers, with the option of using Marvell's firmware or developing custom firmware.

47 Comments

View All Comments

lmcd - Monday, May 31, 2021 - link

If someone's video workflow could be done entirely with Quick Sync, it'd actually be pretty neat -- stuff the whole thing in an ITX case with a handle and go full road warrior.nandnandnand - Thursday, May 27, 2021 - link

I predict that most Alder Lake buyers will use DDR4 instead of DDR5 and no PCIe 5.0.Spunjji - Friday, May 28, 2021 - link

It's a pretty safe bet - there aren't likely to be consumer PCIe 5.0 devices for at least the first 6 months after launch, if not a full year, and even then they're probably not going to be relevant for 95% of consumer use cases. It'll be interesting to see how quickly GPU makers change across, given that even PCIe 4.0 isn't needed yet.haukionkannel - Friday, May 28, 2021 - link

First pci 5.0 gpus 10 years from now? At earliest 4 years… unless we get 8 lines highend gpus… that would cut costs somewhat…mode_13h - Saturday, May 29, 2021 - link

> First pci 5.0 gpus 10 years from now? At earliest 4 years…Pretty much.

5080 - Thursday, May 27, 2021 - link

Interesting, PCIe 5.0 but support for cache with DDR4 and not DDR5 with integrated ECC?Billy Tallis - Thursday, May 27, 2021 - link

SSDs usually don't need bleeding edge DRAM. FTL table lookups don't use much bandwidth, and even slow DRAM has much better latency than NAND flash. They also don't need the huge capacity of server DIMMs; just 1GB per 1TB of NAND. Typical datacenter SSDs are still in the low TBs range, though capacities are going up as new interfaces allow for higher per-drive performance.Also, the on-die ECC in DDR5 and other recent DRAMs is no substitute for the explicit ECC that comes from using a 72-bit bus instead of 64-bit. The latter is a hard requirement for the end-to-end error correction that enterprise SSDs need to provide.

KarlKastor - Thursday, May 27, 2021 - link

Where is the difference of ECC we know from actual DIMM from that on-die ECC of DDR5?Billy Tallis - Thursday, May 27, 2021 - link

On-die ECC as used in DDR5 is invisible to the host system. It protects data at rest in the DIMM, but does nothing to protect the data as it is transmitted between the DIMM and the processor. So the data that arrived at the DIMM may have been corrupted before the DDR5 chips could even compute and store their ECC data. Enterprise grade products need ECC protection along the entire data path, which means adding more bits to the data bus.mode_13h - Thursday, May 27, 2021 - link

What's your take on in-band ECC? Do you think it'll displace OOB ECC, for less performance-intensive applications?