Samsung Teases 512 GB DDR5-7200 Modules

by Dr. Ian Cutress on August 22, 2021 1:02 PM EST

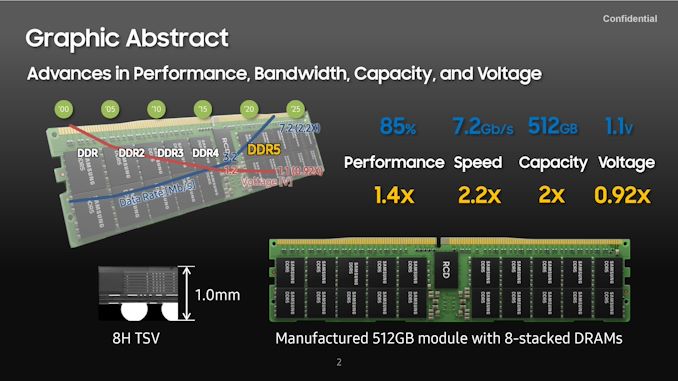

This week as part of the annual Hot Chips semiconductor conference, Samsung’s memory division has presented a poster/slides on a project it is currently working on with impressive end-point results. The company details a 512 GB module of DDR5 memory, running at DDR5-7200, designed for server and enterprise use. This is a step up from the 256 GB modules at the top end of the market today, but to get there, Samsung has been introducing some new features and functionality.

As per standard DDR5 specifications, the modules will run at 1.1 volts with standard JEDEC DDR5-7200 timings, however even JEDEC has not declared an official DDR5-7200 standard at this stage, choosing only to go to DDR5-6400. There are placeholders for future standards, such as DDR5-7200, and based on how the latencies increase from slower speed to higher speed, these should be in the realm of 50-50-50 to 60-60-60*.

*There are three variants for each DDR5 standard – A, B, or C.

DDR5-6400A is 46-46-46 for example, but

DDR5-6400C is 56-56-56.

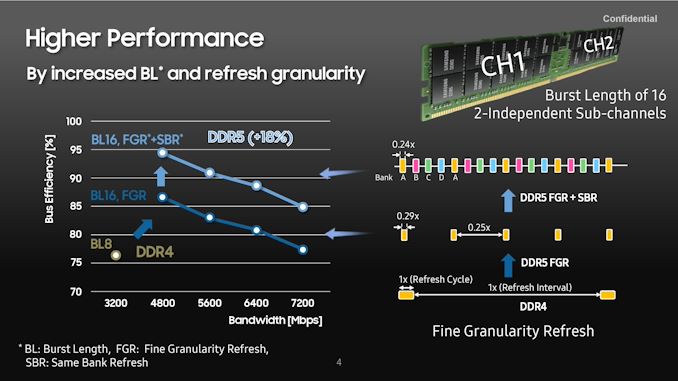

As part of the presentation, Samsung states that the introduction of Same-Bank refresh (SBR) into its DDR5 will increase the efficiency of the DRAM bus connectivity by almost 10%, with DDR4-4800 showing the best efficiency in terms of energy from bit.

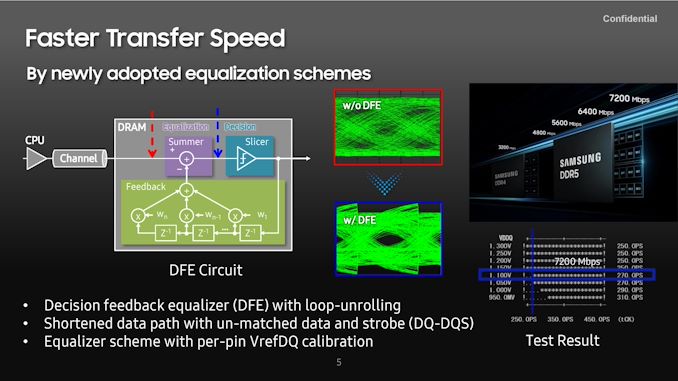

In order to support the higher memory transfer rates of DDR5, Samsung has introduced a new DFE (Decision Feedback Equalizer) for better signal stability. It allows for a more variable data-path location, as well as per-pin calibration techniques.

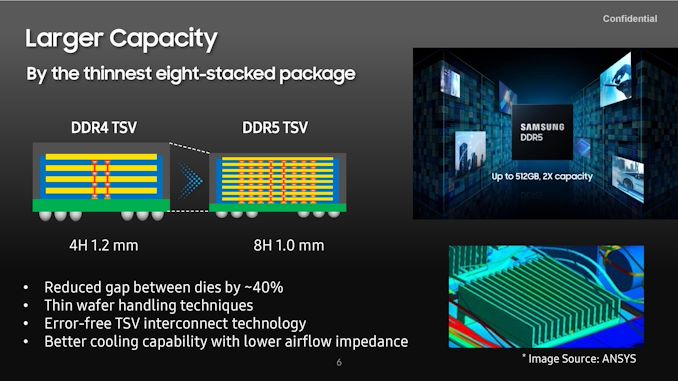

One of the big things about increasing capacity in memory is that you end up stacking more memory together. For their part, Samsung is stating that they can stack 8 DDR5 dies together and still be smaller than 4 dies of DDR4. This is achieved by thinning each die, but also new through-silicon-via connection topographies that allow for a reduced gap between dies of up to 40%. This is partnered by new cooling technologies between dies to assist with thermal performance.

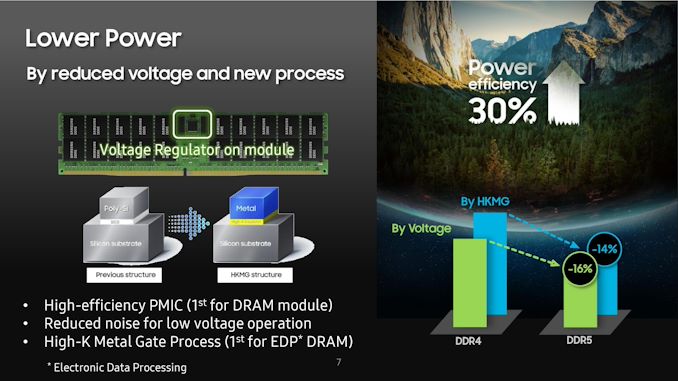

On power, we’ve known that one of the drivers for JEDEC’s newest memory specifications is lower power, and for DDR5 the major thing aside from the lower voltage is to bring the voltage regulator from the motherboard on to the memory module. This allows for the memory module manufacturer to more tightly control the power requirements and consumption of the memory, especially should the motherboard be a very cheap model that might skimp on valued components at the voltage regulation level. For this 512 GB module, Samsung is using a high-efficiency Power Management IC (PMIC) – Samsung as a company has a lot of PMIC experience through its other electronic divisions, so no doubt they can get high efficiency here. Samsung also states that its PMIC has reduced noise, allowing for lower voltage operation, and also uses a High-K Metal Gate process (introduced on CPUs at 45nm) in a first for DRAM.

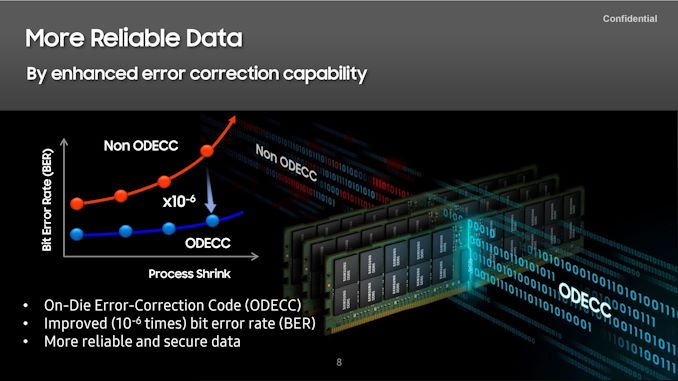

One of the talking points on DDR5 has been the on-die ECC (ODECC) functionality, built in to DDR5 to help improve yields of memory by initiating a per-die ECC topology. The confusion lies in that this is not a true ECC enablement on a DDR5 module, which still requires extra physical memory and a protected bus. But on the topic of ODECC, Samsung is showcasing an improvement on its bit-error rate of 10-6, or a factor of a million lower BER. How much of this is required by the DDR5 JEDEC specification is unclear at this point, but it’s still a good direction to have.

At the end of the slide deck from Samsung, it states that its first 512 GB module should be ready for mass production by the end of 2021 – it’s unclear if this is a DDR5-7200 module or something else, as the slide could be interpreted differently. But one of the key aspects to this discussion is when the market expects the crossover of DDR4 and DDR5 to occur: Samsung has a big window of 2023-2024 planned for that crossover, which does align with other market analyst predictions.

This stuff is still going to cost some serious money, which makes me wonder what this means for consumers. Right now the supply of 32 GB modules (UDIMMs) seems to be plentiful for those that want 128 GB of memory in a consumer system. The advent of these new memory packages from Samsung might suggest a path to 64 GB modules for DDR5 on the consumer platform, however you can bet your bottom dollar that they’ll stay for enterprise for a while as they will command a price premium.

Stay tuned for AnandTech’s Hot Chips content throughout this week.

27 Comments

View All Comments

Small Bison - Sunday, August 22, 2021 - link

Because the operations take place over many cycles. A typical 128 bit interface is only transferring 16 bytes of data at a time. Waiting 50 cycles isn’t that big of a deal when it takes 65 *thousand* cycles to transfer just one MiB of data.We’ve had this latency discussion with every new version of DDR. CAS latency has always been in the 5-8 ns range, and people repeatedly trip up, comparing low latency, overclocked RAM from the previous generation against more conservative server RAM & JEDEC specifications for the new generation.

willis936 - Sunday, August 22, 2021 - link

Ceteris paribus, the CAS should be around 32 at this speed to have parity with current mainstream DDR4 latency. What happens every DDR version is that it takes 1-2 years for SKUs to match the latency performance of the previous DDR version. Is it ever a big deal? Not enough for anyone to choose to make a new system on an old platform. Thankfully we're seeing a focus on large LL cache just before DDR5.Brane2 - Monday, August 23, 2021 - link

Except that:1. With each generation this is further away from being RANDOM Acces Memory.

2. Access time latency IS a bottleneck. Most of the other accesses are being taken care by the cache and prefetchers. It is whatever misses them that will cause massive stalls.

3. Your example is mostly irrellevant. Programs access data in far smaller chinks than 1MB. And when they do gulp it in Megabytes, they use non-cached access for one-time use. So, such linear, "drag-strip" use is relatively rare.

cp0x - Sunday, August 29, 2021 - link

If you only had one core, that might be important.Today's machines bottleneck on the bus, and cores are quickly bandwidth starved to DRAM. High level languages make it even worse (slab allocators mean that nothing is ever in cache).

So if we want more than 4-8 cores (8-16 threads) to be running at speed, we need a lot more bandwidth.

Kamen Rider Blade - Sunday, August 22, 2021 - link

The amount of time in each cycle isn't consistent as you go up in Clock Speed.For DDR4, you should use a table to help figure out the true Effective Latency:

https://www.reddit.com/r/pcmasterrace/comments/cd2...

You'll need a new Table for DDR5 RAM effective Latency as well

Silver5urfer - Sunday, August 22, 2021 - link

We have to wait for 3-6 years minimum to get a solid spec DDR5, look how long it took for DDR4 to reach to it's maximum potential. Now in 2021 we have DDR4 4000MHz C15 Dual Rank B-Die kits, that too at high 1.5v.Kamen Rider Blade - Sunday, August 22, 2021 - link

That's why I'm not in a rush to DDR5hansmuff - Sunday, August 22, 2021 - link

True enough. I'm not looking at DDR5 before 2024.Wereweeb - Monday, August 23, 2021 - link

Having enough bandwidth for your application, and a large enough DRAM cache so that you don't need to tap into NAND, are much more important than having the lowest latency.Brane2 - Monday, August 23, 2021 - link

Meaningless marketing cr*p.Who cares about inter-die distance etc.

Waht I want to know is what doe they intend to do about FRIGGIN CL=56.

56 cycles to start reading a row.

Yes, it's at 7200MHz, but still.

Speeding up transfers doesn't mean that much if real latency is the same or worse...

Same for the rest of the cr*p. ODECC isn't there because they just needed to do some cool stuff.

It's there because with higher density cell reliability sucks, so they had to do something about it.

And they did the minimum that they can get away with.

So they shouldn't be selling it as something "extra".