Apple Announces M2 SoC: Apple Silicon for Macs Updated For 2022

by Ryan Smith on June 6, 2022 5:30 PM EST

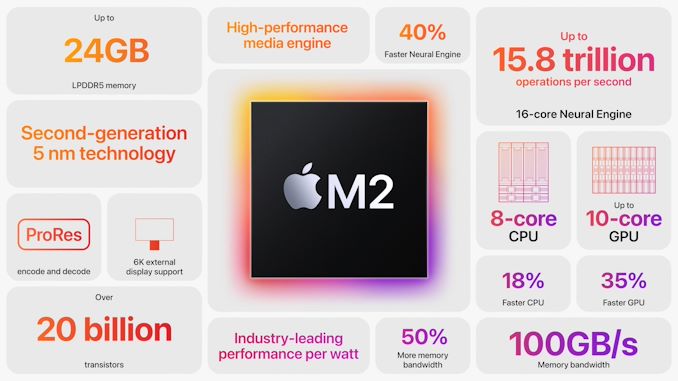

Though primarily a software-focused event, Apple’s WWDC keynotes are often stage for an interesting hardware announcement or two as well, and this year Apple did not disappoint. At the company’s biggest Mac-related keynote of the year, Apple unveiled the M2, their second-generation Apple Silicon SoC for the Mac (and iPad) platform. Touting modest performance gains over the original M1 SoC of around 18% for multithreaded CPU workloads and 35% in peak GPU workloads, the M2 is Apple’s first chance to iterate on their Mac SoC to incorporate updated technologies, as well as to refresh their lower-tier laptops in the face of recent updates from their competitors.

With the king of the M1 SoCs, M1 Ultra, not even 3 months behind them, Apple hasn’t wasted any time in preparing their second generation of Apple Silicon SoCs. To that end, the company has prepared what is the first (and undoubtedly not the last) of a new family of SoCs with the Apple Silicon M2. Designed to replace the M1 within Apple’s product lineup, the M2 SoC is being initially rolled out in refreshes of the 13-inch MacBook Pro, as well as the MacBook Air – which is getting a pretty hefty redesign of its own in the process.

The launch of the M2 also gives us our first real glimpse into how Apple is going to handle updates within the Apple Silicon ecosystem. With the iPhone family, Apple has kept to a yearly cadence for A-series SoC updates; conversely, the traditional PC ecosystem is on something closer to a 2-year cadence as of late. M2 seems to split this down the middle, coming about a year and a half after the original M1 – though in terms of architecture it looks closer to a yearly A-series SoC update.

From a high level, there has been a limited number of changes with the M2 – or at least as much as Apple wants to disclose at this time – with the focus being on a few critical areas, versus the bonanza that was the initial M1 SoC. While all of this is preliminary ahead of either further disclosures from Apple or getting hands-on time with the hardware itself, the M2 looks a lot like a derivate of the A15 SoC, similar to how the M1 was derived from A14. As a result, at first glance the M1 to M2 upgrade looks quite similar to the A14 to A15 upgrade.

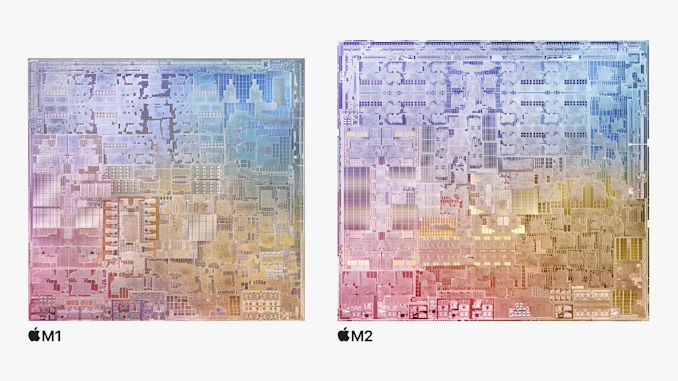

According to Apple, the new SoC is comprised of roughly 20 billion transistors, which is 4B (25%) more than the original M1 – and 5B more than the A15 SoC. The chip is being made on what Apple terms a “second generation 5nm” process, which we believe is likely TSMC’s N5P line, the same line used for the A15 SoC. N5P offers improved performance characteristics versus N5, but not density improvements. So while Apple doesn’t disclose die sizes, the company’s side-by-side die shots are at least accurate in that M2 is going to be a bigger chip than M1.

| Apple Silicon SoCs | |||

| SoC | M2 | M1 | |

| CPU | 4x High Performance (Avalanche?) 16MB Shared L2 4x High Efficiency (Blizzard?) 4MB Shared L2 |

4x High Performance (Firestorm) 12MB Shared L2 4x High Efficiency (Icestorm) 4MB Shared L2 |

|

| GPU | "Next Generation" 10-Core 3.6 TFLOPS |

8-Core 2.6 TFLOPS |

|

| Neural Engine | 16-Core 15.8 TOPS |

16-Core 11 TOPS |

|

| Memory Controller |

LPDDR5-6400 8x 16-bit CH 100GB/sec Total Bandwidth (Unified) |

LPDDR4-4266 8x 16 CH 68GB/sec Total Bandwidth (Unified) |

|

| Memory Capacity | 24GB | 16GB | |

| Encode/ Decode |

8K H.264, H.265, ProRes, ProRes RAW |

4K H.264, H.265 |

|

| USB | USB4/Thunderbolt 3 2x Ports |

USB4/Thunderbolt 3 2x Ports |

|

| Transistors | 20 Billion | 16 Billion | |

| Mfc. Process | "Second Generation 5nm" TSMC N5P? |

TSMC N5 | |

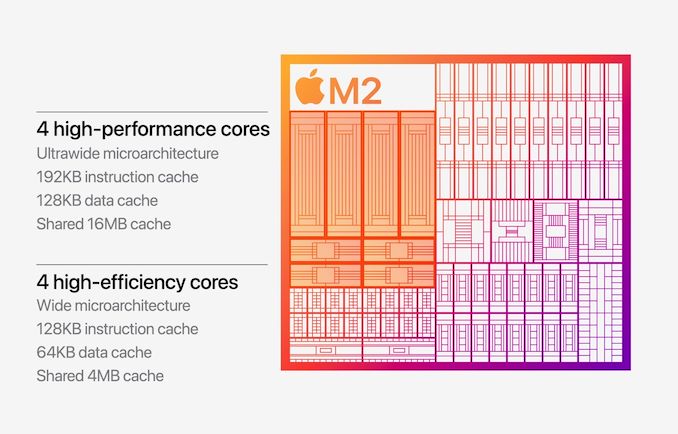

Starting from the top, in terms of their Arm-architecture CPU cores, the M2 retains Apple’s 4 performance plus 4 efficiency core configuration. Apple is not disclosing what generation CPU cores they’re using here, but based on the performance expectations and timing, there’s every reason to believe that these are the Avalanche and Blizzard cores that were first introduced on the A15.

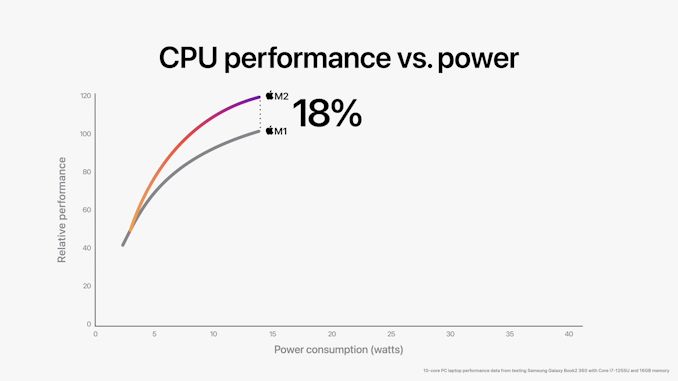

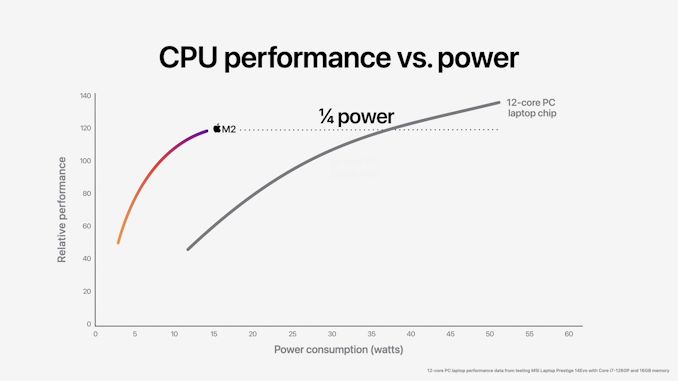

With regards to performance, Apple is saying that the M2 offers 18% improved multi-threaded CPU performance versus the M1. The company does not offer a breakdown of clockspeeds versus IPC gains, but if our hunch about M2 being Avalanche/Blizzard is correct, then we already have a good idea of what the breakdown is. Relative to the Firestorm core in the A14/M1, Avalanche offers only modest performance gains, as Apple invested most of their improvements into improving overall energy efficiency. As a result, the bulk of the performance gains there come from increased clockspeeds rather than IPC improvements.

The performance CPU cores on M2 also come with a larger pool of L2 cache, which also serves to improve performance. Whereas M1 had 12MB of L2 cache shared among the cores, M2 brings this up to 16MB, a 4MB increase over both the M1 and for that matter the A15.

Based on what we’ve already seen with the A15, this bigger update in this generation is on the efficiency core side of matters. The Blizzard CPU cores are increasingly behaving like not-so-little cores, offering relatively high performance and a much wider backend design than what we see with other Arm efficiency cores. Among other things, Blizzard added a fourth Integer ALU, which combined with other changes gave A15 a significant (28%) performance increase in those cores. Carried over to M2, and it’s not unreasonable to expect similar gains, though the wildcard factor will be what clockspeeds Apple dials things to.

This, in turn, is also seemingly why Apple has decided to focus on MT performance for their Apple-to-Apple comparison. With the largest performance gains coming courtesy of the efficiency cores, in performance-bound situations it’s MT workloads which get to tap the E cores alongside the P cores that would see the greatest performance improvements. On the whole, Avalanche/Blizzard made for a modest year on the CPU microarchitecture front, and that looks to be carrying over for the M2 SoC.

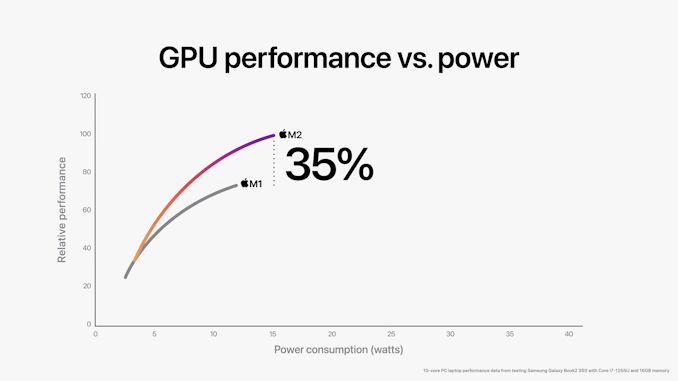

Meanwhile on the GPU front, Apple is going bigger. Though reclusive as always about the underlying architecture – merely calling this a “next generation” GPU – M2 comes with 10 GPU cores baked in, up from 8 on the M1. Officially, this GPU is rated for 3.6 TFLOPS, which is a 1 TFLOPS more than the 8 core M1. As well, the new GPU comes with a larger shared L2 cache, though Apple isn’t disclosing the cache size there.

With a combination of a larger core count and what would seem to be a 10% or so increase in GPU clockspeeds (based on TFLOPS), Apple is touting two performance figures for the M2’s GPU. At iso-power (~12W), the M2 should deliver 25% faster GPU performance than the M1. However the M2’s GPU can, for better or worse, also draw more power than the M1’s GPU. At its full power state of 15 Watts, according to Apple is can deliver 35% more performance.

Overall this indicates that while Apple has been able to improve their energy efficiency – GPUs love running wide and slow – Apple’s peak GPU power consumption is going up. This should have minimal impact on light workloads, but it will be interesting to see what it means for relatively heavy and constant workloads, especially on the fanless MacBook Air. Meanwhile the GPU’s display controller remains seemingly unchanged, topping out at 6K for external monitors.

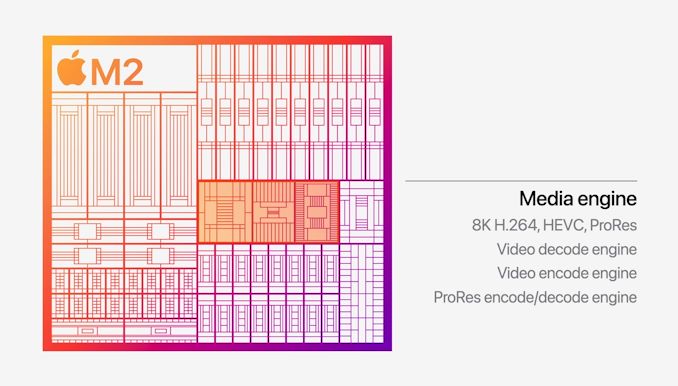

Tangential to the GPU updates, M2 also comes with an updated video encode/decode block, which at first glance looks a lot like a pared-down version of the block used on the M1 Pro/Max. Those SoCs added support for Apple’s ProRes and ProRes RAW codecs, and that support has now filtered back down into the base M2 SoC. As well, Apple is now officially supporting 8K video decode on the M2, whereas the M1, though never having an official resolution designation, was essentially a 4K part.

Finally, on the processing side of matters, the M2 is inheriting the A15’s updated neural engine. According to Apple, this is still a 16-core design, and it happens to have the same 15.8 trillion operations per second (TOPS) rating as the A15’s neural engine. Which, despite only being on par with the A15, still makes it 40% faster than the M1’s neural engine, which topped out at 11 TOPS.

Altogether, Apple is projecting a great deal of confidence in the performance of their second-generation Apple Silicon chip, and even more so its competitiveness versus Intel. While we’ll have to wait to get our hands on the hardware to confirm its performance, the M1 certainly lived up to claims there. So the expectations for M2 are similarly high.

Memory: LPDDR5-6400, Up To 24GB

While the core logic of Apple’s latest SoC would seem to be largely an enhanced version of the A15, it does have one very notable feature advantage: LPDDR5 support.

Whereas the vanilla M1 (and the A15) only supported LPDDR4x memory, the M2 supports the newer LPDDR5 memory standard. The biggest change of which is support for much higher memory clockspeeds; based on Apple’s figures, the M2 is running at 6400Mbps/pin (LPDDR5-6400), which is up significantly from the 4266Mbps/pin (LPDDR4x-4266) memory clockspeeds of the original M1. The net result is that, on the SoC’s 128-bit memory bus, the M2 has 100GB/second of memory bandwidth to play with, a 50% increase over the M1 (~68GB/sec).

Apple’s unconventional use of memory technologies remains one of their key advantages versus their competitors in the laptop space, so a significant increase in memory bandwidth helps Apple to keep that position. Improvements in memory bandwidth further improve every aspect of the SoC, and that especially goes for GPU performance, where memory bandwidth is often a bottlenecking factor, making the addition of LPDDR5 a key enabler for the larger, 10-core GPU. Though in this case, it's the M2 playing catch-up in a sense: the M1 Pro/Max/Ultra all shipped with LPDDR5 support first, the M2 is actually the final M-series chip/tier to get the newer memory.

Past that, Apple is once again placing their LPDDR5 memory packages on-chip with the processor die itself. So each M2 chip will need to be equipped with memory ahead of time, and the device supply is likely to fluctuate a bit based on memory capacity depending on what the most popular configurations are, especially early on.

M2 devices are available with either, 8GB, 16GB, or 24GB of memory. Given that Apple is still using just two stacks of memory, it looks like the company is finally taking advantage of LPDDR’s support for non-power-of-two die sizes (e.g. 12Gb dies), which allows them to get 12GB of memory into a single package without any further shenanigans. And assuming Apple replicates this down the line for the obligatory Pro/Max/Ultra SoCs, we should see the top memory capacities of all of Apple’s SoCs increase by 50% over the previous generation.

And the Rest: Updated ISP, Same USB

Rounding out today’s M2 announcement, there are a couple more items that warrant a quick call-out.

First, the M2 is getting an updated ISP as well as an updated Secure Enclave. Like other aspects of M2, these are likely inherited from the A15, which received similar updates as well.

Meanwhile, a look at the specs of the new MBA and MBP indicate that there haven’t been any notable changes in USB or other I/O support for the new SoC. M1 was already at the top of the curve in 2020 when it launched with USB4 support, so nothing has changed here. This does mean, however, that the SoC is seemingly still limited to Thunderbolt 3 support, despite the fact that Thunderbolt 4 has now been out for well over a year. Both the MBA and MBP are also shipping with two USB ports, so it would seem that’s still the native limit of the SoC.

Apple also hasn’t talked at all about PCIe capabilities. We’ll know more once we have the hardware in-hand, but at least for now there’s no reason to believe that Apple has added PCIe 5 support or changed the number of lanes available. I/O has remained something of a constraining factor for the entire Apple Silicon family, so it does make me wonder about what this means for the eventual Apple Silicon Mac Pro.

Available in July

Closing out today’s announcement, the M2 will be shipping in the new 2022 MacBook Air, as well as the refresh 2022 12-inch MacBook Pro. According to Apple, those devices will be available in July, with pre-orders open today.

In the meantime, the M1 isn’t going anywhere. Besides being at the heart of the Mac Mini – which didn’t receive an update today – Apple is keeping the 2020 M1-based MacBook Air around. So both versions of the entry-level M-series SoC will be sticking around for some time to come.

171 Comments

View All Comments

Otritus - Tuesday, June 7, 2022 - link

There are 2 different transistors that can be counted. Schematic or layout if I recall correctly. Schematic transistors are the transistors in the design blueprints, and layout transistors are the transistors physically put on the processor. Transistors are not counted, but estimated instead. If I recall correctly there was an Intel product with 1.2B schematic and 1.4B layout transistors (Either Ivybridge-S or Haswell-S). Sandybridge-S had 956M schematic and over 1B layout transistors. They should be within 10-20% of each other. Regardless of methodology Apple is definitely providing more transistors in M2 than AMD or Intel.ballsystemlord - Tuesday, June 7, 2022 - link

Thanks! That explains it nicely.boozed - Thursday, June 9, 2022 - link

It's fascinating that they wouldn't know exactly how many transistors their designs contain.Do they conduct their simulations on simplified versions of the circuits?

jab701 - Thursday, September 8, 2022 - link

When you layout a design you might need buffers to help drive signals further across the chip, these are not functional, they wont be written in the design but are required to make the design work in a physical sense.The clock distribuition network for exaample, we know where the clock is going to go but we wont know how it needs to be balanced until we go from verilog design into physical design.

We also sometimes will duplicate logic etc in order to get a working physical design.

Dolda2000 - Thursday, June 9, 2022 - link

A transistor isn't really a transistor for a multitude of reasons.For one thing, they can differ in geometry (and size) in order to obtain different tradeoffs in terms of switching speed, leakage current, gate capacitance and other metrics, and one IC design often uses many different transistor designs for different parts of the design.

For another thing, it is common for several transistors to share various parts, such as one gate serving to switch several different channels, which saves space compared to having the same number of distinct transistors.

Various such aspects can be seen making a very distinct difference to total density; for instance, GPUs often pack a significantly larger number of transistors into the same area as a CPU (even on the same process), because it uses different designs to achieve different goals.

zamroni - Tuesday, June 7, 2022 - link

transistor count very correlates to performance, and it's lineary in most cases.more caches, cpu pipelines, gpu alu need more transistors.

SunMaster - Wednesday, June 8, 2022 - link

By your logic the CPU with the most transistors is the fastest. Why do we need AMD and Intel anyway, it's just to make sure enough transistors get manufactured on a large enough die....zamroni - Friday, July 1, 2022 - link

basically yes by increasing parallelism because pushing for higher frequency is much harder to be done.zamroni - Friday, July 1, 2022 - link

rtx 3090 is faster than 3070 because 3090 has more cores.5950x is faster than 5800* in multithreading because of more cores.

more cores, more transistor.

for cpu, single core performance improvement today is mostly done by lengthening branch prediction which needs bigger caches.

more caches, more transistors

mode_13h - Monday, July 4, 2022 - link

> single core performance improvement today is mostly done by lengthening> branch prediction which needs bigger caches.

LOL. You're joking, right?

Intel and AMD put lots of effort into making their cores faster, and it's achieved by the sum of very many individual tweaks and changes. Try going back and reading the Deep Dive coverage on this site of all the new cores that have been introduced over the past 5 years.

The other thing you're missing is that new process nodes don't only increase transistor counts, they also move the transistors closer together. This enables longer critical paths, in terms of the numbers of transistors to be chained together, for a given clock frequency. That, in turn, allows the complexity of pipeline stages to be increased, which can result in fewer of them. Or, you can have the same number of pipeline stages, but they can have more complexity than before.