PCI-SIG Finalizes PCIe 5.0 Specification: x16 Slots to Reach 64GB/sec

by Ryan Smith on May 29, 2019 6:30 PM EST

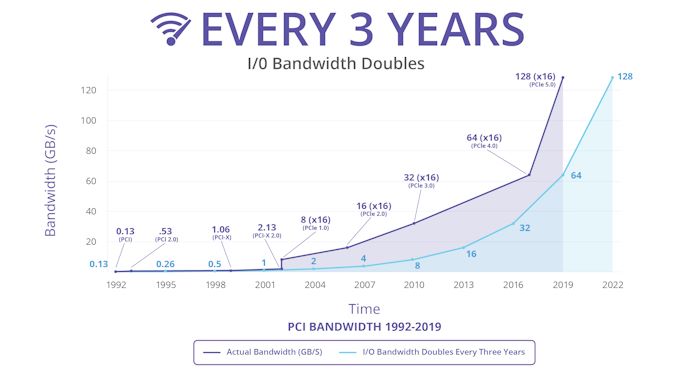

Following the long gap after the release of PCI Express 3.0 in 2010, the PCI Special Interest Group (PCI-SIG) set about a plan to speed up the development and release of successive PCIe standards. Following this plan, in late 2017 the group released PCIe 4.0, which doubled PCIe 3.0’s bandwidth. Now less than two years after PCIe 4.0 – and with the first hardware for that standard just landing now – the group is back again with the release of the PCIe 5.0 specification, which once again doubles the amount of bandwidth available over a PCI Express link.

Built on top of the PCIe 4.0 standard, the PCIe 5.0 standard is a relatively straightforward extension of 4.0. The latest standard doubles the transfer rate once again, which now reaches 32 GigaTransfers/second. Which, for practical purposes, means PCIe slots can now reach anywhere between ~4GB/sec for a x1 slot up to ~64GB/sec for a x16 slot. For comparison’s sake, 4GB/sec is as much bandwidth as a PCIe 1.0 x16 slot, so over the last decade and a half, the number of lanes required to deliver that kind of bandwidth has been cut to 1/16th the original amount.

The fastest standard on the PCI-SIG roadmap for now, PCIe 5.0’s higher transfer rates will allow vendors to rebalance future designs between total bandwidth and simplicity by working with fewer lanes. High-bandwidth applications will of course go for everything they can get with a full x16 link, while slower hardware such as 40GigE and SSDs can be implemented using fewer lanes. PCIe 5.0’s physical layer is also going to be the cornerstone of other interconnects in the future; in particular, Intel has announced that their upcoming Compute eXpress Link (CXL) cache coherent interconnect will be built on top of PCIe 5.0.

| PCI Express Bandwidth (Full Duplex) |

|||||||

| Slot Width | PCIe 1.0 (2003) |

PCIe 2.0 (2007) |

PCIe 3.0 (2010) |

PCIe 4.0 (2017) |

PCIe 5.0 (2019) |

||

| x1 | 0.25GB/sec | 0.5GB/sec | ~1GB/sec | ~2GB/sec | ~4GB/sec | ||

| x2 | 0.5GB/sec | 1GB/sec | ~2GB/sec | ~4GB/sec | ~8GB/sec | ||

| x4 | 1GB/sec | 2GB/sec | ~4GB/sec | ~8GB/sec | ~16GB/sec | ||

| x8 | 2GB/sec | 4GB/sec | ~8GB/sec | ~16GB/sec | ~32GB/sec | ||

| x16 | 4GB/sec | 8GB/sec | ~16GB/sec | ~32GB/sec | ~64GB/sec | ||

Meanwhile the big question, of course, is when we can expect to see PCIe 5.0 start showing up in products. The additional complexity of PCIe 5.0’s higher signaling rate aside, even with PCIe 4.0’s protracted development period, we’re only now seeing 4.0 gear start showing up in server products; meanwhile the first consumer gear technically hasn’t started shipping yet. So even with the quick turnaround time on PCIe 5.0 development, I’m not expecting to see 5.0 show up until 2021 at the earliest – and possibly later than that depending on just what that complexity means for hardware costs.

Ultimately, the PCI-SIG’s annual developer conference is taking place in just a few weeks, on June 18th, at which point we should get some better insight as to when the SIG members expect to finish developing and start shipping their first PCIe 5.0 products.

Source: PCI-SIG

55 Comments

View All Comments

kn00tcn - Friday, May 31, 2019 - link

because games aren't raw data...! shaders need compilation, gpu usage goes up, cpu usage goes up, assets get uncompressed from archives, in rare cases vsync/fps cap limits loading speed, in other cases the engine is too single threadeddid you not notice nvidia, amd, AND steam added cached shaders features that explicitly state they improve loading time?

there's no hidden bottleneck, it already is being addressed by engineers on multiple sides

mode_13h - Friday, May 31, 2019 - link

I think PCIe 4.0 could reduce latency for VR use cases. That's the main consumer GPU use case I see for it... for those consumers using VR, anyhow. I don't know how much that would really carry over to PCIe 5, though.I'm not saying it won't affect frame rates (esp. 99th percentile) at the margins, but we're not talking about a big impact at x16 connectivity.

Since we know Intel is using CXL for datacenter GPUs and that CXL can work atop PCIe 5, it will be interesting to see if Intel provides this to consumers, in some premium Titan-like product.

stancilmor - Monday, June 3, 2019 - link

There is definitely some hidden bottleneck. My rig has 32 GB RAM and back when games were less than 24 GB, I created a RAM 24 GB RAM drive and loaded the entire game to the RAM drive. This still left 8 GB for system RAM at a time when 2GB was more than enough. Anyway even loading from the RAM drive the game didn't seem to load any faster. Back then I blamed it on my internet connect / ping / latency. Now days I have a fiber optic link to the internet, but I'm not convinced the network speed is the bottleneck. Could be protocol overhead and how Windows transfers data?rtho782 - Thursday, May 30, 2019 - link

No, but given that such GPUs can cope with a PCIe 3.0 x8 link easily, they will be able to cope with a PCIe 5.0 x2 link.Other devices like hard drive controllers that previously needed to be x4 or x8 can now be x1 or x2.

Suddenly the 20 lanes from your CPU can go a lot further.

mode_13h - Thursday, May 30, 2019 - link

This is basically my point, except I wouldn't say that RAID controllers will get much narrower, depending on whether it's a SSD RAID or not. If SSD, then you'll probably need the additional bandwidth.However, for HDD RAIDs, practical limits on RAID sizes would mean that controllers' interfaces will probably be cut in half.

deil - Thursday, May 30, 2019 - link

no, but ssd that could saturate that slot would be fun.We ALREADY have 90% used on 5GB/s Corsair SSD and its YET unreleased to masses.

10GB/s SSD from PCIE5.0 would be insane.

Someguyperson - Wednesday, May 29, 2019 - link

It seems a bit odd, but that graph is actually putting the bandwidth gains in a very positive light. If you plot those points in a log scale, PCIe bandwidth has fallen short of the historical trend from 2014 until this announcement. This announcement puts everything back on track, but if you go by the "doubling every 3 years" like in the slides, PCIe 6.0 should have come out last year with a max bandwidth of ~128 GB/sec.The Hardcard - Wednesday, May 29, 2019 - link

There were several articles in the recent past claiming that PCIe 4.0 would be too expensive for the mainstream. So it’ll be interesting to see the price difference for motherboards and cards.sorten - Wednesday, May 29, 2019 - link

That's odd. It'll be a feature of every AMD motherboard moving forward until it's replaced with 5.0.imaheadcase - Wednesday, May 29, 2019 - link

What is odd? It is expensive on the AMD motherboards. Just how it is.